If a tree falls in a forest with no one around to hear it, does it still make a sound?

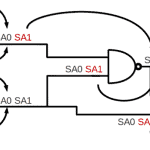

If a fault occurs in a combinational circuit but its masked at the outputs is it still a fault?

If you can’t excite a fault from the circuit inputs does it really exist?

If you can’t propagate a fault to an output pin, does it matter?

In assessing an integrated circuit’s testability engineers consider the concepts of controllability and observability. In these specific characteristics of testability came up often the academic test literature of the 1970’s and 1980’s. The challenge back then was automatic test generation and fault simulation. [Read more…]